CNCERT牵头首个处理器芯片硬件安全评估国家重点研发计划项目

摘要:

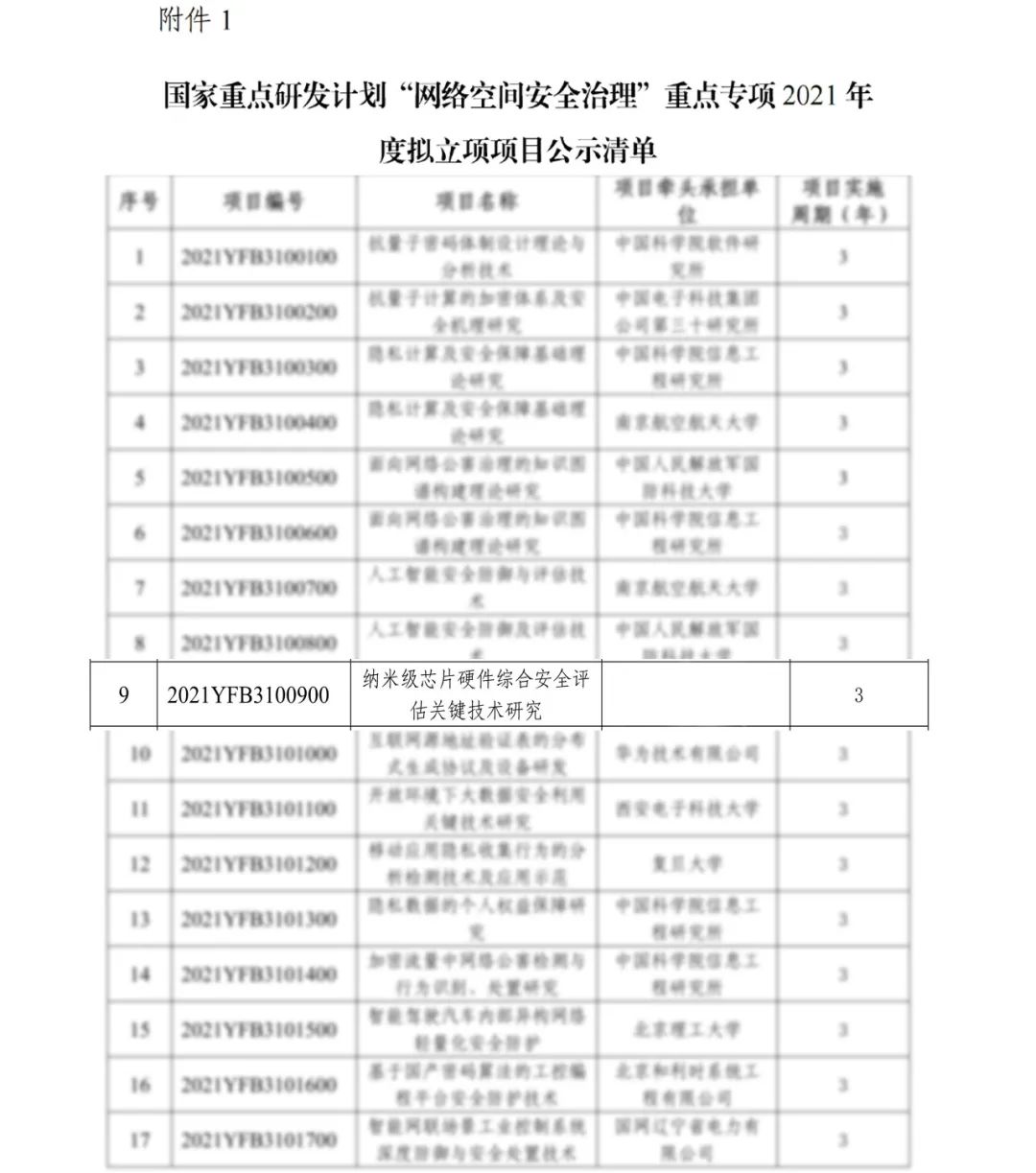

2021年12月3日,科技部公示了国家重点研发计划“网络空间安全治理”重点专项2021年拟立项项目,其中,“纳米级芯片硬件综合安全评估关键技术研究”项目(项目编号:2021YFB3100900)由国家计算机网络应急技术处理协调中心(CNCERT)牵头承担,项目负责人为CNCERT网络安全应急技术国家工程实验室常务副主任何跃鹰。项目联合了清华大学、中国科学院微电子研究所、西北工业大学等本领域顶尖研究团队,重点面向纳米级通用处理器芯片硬件安全问题开展综合评估方法与关键技术研究。

立项背景

“没有网络安全就没有国家安全”,处理器芯片是网络空间安全的最后一道关闸。关键芯片安全可控是我国网络空间安全重要战略需求。聚焦芯片安全核心需求,CNCERT网络安全应急技术国家工程实验室在持续开展物联网安全监测、5G网络安全检测和固件安全检测等研究基础上着力拓展芯片安全检测研究方向,承担了工业互联网创新发展工程“嵌入式芯片安全检测平台”等项目研发工作。

Intel和ARM处理器“熔断”和“幽灵”漏洞爆出后,处理器芯片安全问题更引起相关部门高度重视。立足国家战略,科技部2021年国家重点研发计划“网络空间安全治理”专项设立“纳米级芯片/硬件综合安全评估技术”项目。

项目简介

2021年12月3日,科技部公示国家重点研发计划“网络空间安全治理”重点专项2021年拟立项项目,其中,“纳米级芯片硬件综合安全评估关键技术研究”项目(项目编号:2021YFB3100900)由国家计算机网络应急技术处理协调中心牵头承担,项目负责人为CNCERT网络安全应急技术国家工程实验室常务副主任何跃鹰。

研究内容

“纳米级芯片硬件综合安全评估关键技术研究”项目是科技部在通用处理器、纳米级芯片和网络安全评估交叉领域的首个重点专项,为期三年,重点面向纳米级通用处理器芯片硬件安全问题开展综合评估方法与关键技术研究,拟提出集成电路设计(RTL/门级)、微体系结构和芯片外部端口三个层面的安全脆弱性检测方法、逆向分析方法,研制一系列工具,构建纳米级芯片硬件安全综合评估平台,在国产处理器厂商开展示范应用,有力支撑我国自主设计处理器安全性全面提升。

项目的具体研究内容如下:

(1)处理器集成电路设计安全脆弱性检测方法研究:研究基于仿真测试、形式化验证和结构特征分析的安全检测技术;研究基于形式化模型实现设计中时间、能量和电磁侧信道检测技术;研究与主流EDA工具及设计流程融合的白盒安全检测技术;研究处理器设计加速仿真技术。

(2)处理器微体系结构脆弱性检测方法研究:研究针对通用处理器的自动化安全测试和漏洞挖掘技术,覆盖已发现的主要处理器硬件安全漏洞类型;研究微体系结构漏洞的批量形式化检测和挖掘技术。

(3)处理器芯片运行时动态检测SoC架构研究:研究基于处理器芯片端口行为的硬件漏洞检测技术,支持Intel x86架构的硬件安全漏洞变种检测;研究并提出处理器芯片运行时动态检测SoC架构;研究芯片时间、能量和电磁侧信道脆弱性检测技术。

(4)纳米级处理器芯片微体系结构逆向及底层固件提取技术研究:研究反向图像中MOS管、三极管、电阻、电容等常规器件自动识别技术,研究硬结构加软配置结合的底层固件提取技术。

(5)纳米级芯片硬件安全综合评估平台建设:研究纳米级处理器芯片硬件安全综合评估指标体系,建立国家级处理器硬件安全综合检测与评估平台,可对Intel x86、进口ARM、飞腾(国产ARM)、龙芯、RISC-V等5类主流处理器芯片进行硬件脆弱性检测;建设国家级处理器硬件安全漏洞库。

项目团队

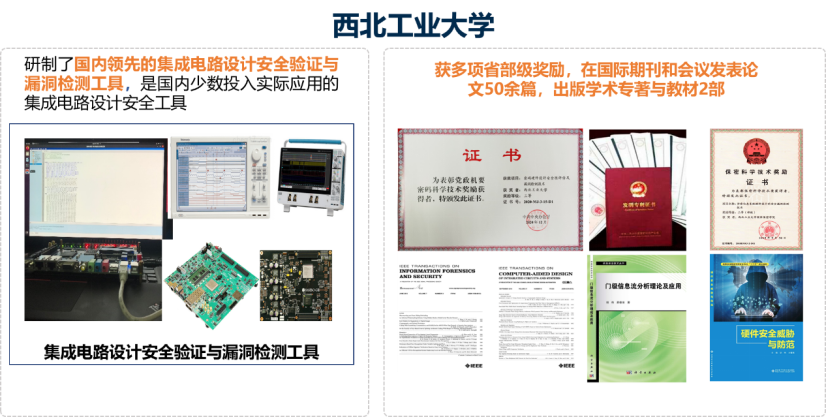

项目联合了清华大学、中国科学院微电子研究所、西北工业大学等本领域顶尖研究团队共同承担研发工作。各课题承担单位、参与单位及负责人情况如下表所示。

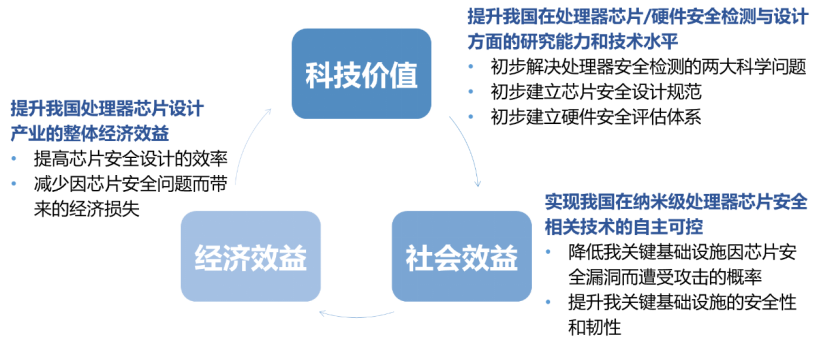

规划愿景

围绕项目目标,项目研究团队将紧密跟踪处理器芯片硬件安全检测、评估、设计科技前沿,面向国家芯片安全可控战略需求,着力实现芯片安全测评技术的创新突破,力图形成科技创新引领产业进步的良性循环,有力支撑国家网络空间安全保护工作。